삼성전자·TSMC, 초미세 대안 '차세대 패키징' 한판 경쟁

타이완세미콘서 'FO-PLP' 기술 부각될 듯

기술 초기단계…삼성·TSMC, 시장 선점 사활

![[서울=뉴시스]삼성전자 평택 캠퍼스 반도체 공장 내부.(사진=삼성전자 제공) photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2022/12/27/NISI20221227_0001163166_web.jpg?rnd=20221227160630)

[서울=뉴시스]삼성전자 평택 캠퍼스 반도체 공장 내부.(사진=삼성전자 제공) [email protected] *재판매 및 DB 금지

아직 양사 모두 이 기술의 공정 도입을 위해 개발 단계인데, 기존보다 적은 비용으로 대량의 반도체를 양산할 수 있는 만큼 이번 포럼에서 고객사 확보에 집중할 방침이다.

21일 업계에 따르면 내달 초 대만에서 열리는 반도체 포럼 '세미콘 타이완 2024'에서 주요 반도체 기업들은 FO-PLP 기술을 집중적으로 공개한다.

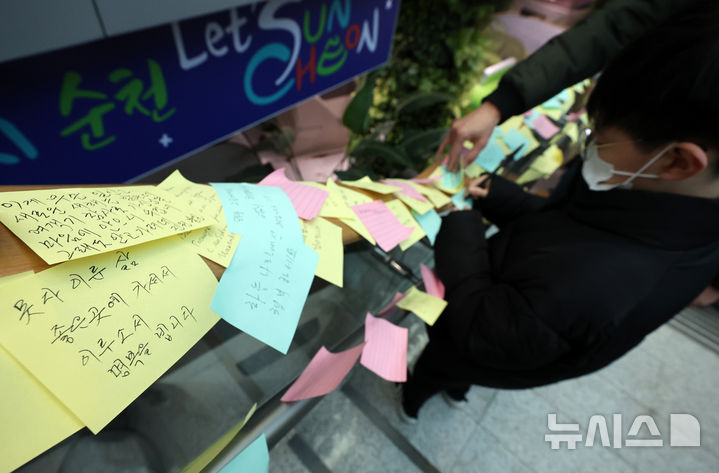

FO-PLP는 기존의 원형 웨이퍼를 대체하기 위해 직사각형 인쇄회로기판(PCB) 패키징을 도입한 첨단 패키징 기술이다. 생산 효율이 높고, 비용을 절감할 수 있어, 첨단 반도체 생산능력을 결정짓는 핵심 기술로 꼽힌다.

최근 1나노 이하 초미세공정이 기술적 한계에 직면하자 삼성전자와 TSMC는 FO-PLP 등 첨단 패키징 기술을 끌어올려 반도체 성능을 높이는데 주력하고 있다.

이에 삼성전자는 이번 포럼에서 고대역폭메모리(HBM)과 함께 FO-PLP를 핵심 기술로 꺼내들 가능성이 높다. 삼성전자 경영진이 포럼의 기조연설을 직접 맡을 것으로 예상되는데 자사 FO-PLP 경쟁력을 중점적으로 강조할 전망이다.

삼성전자는 이미 지난 2019년 삼성전기로부터 FO-PLP 사업을 인수해 상용화에 성공하면서 기술력에서는 TSMC보다 한 수 위라는 평가를 받는다.

하지만 삼성전자는 아직 이 기술을 일부 공정에만 활용하고 있어, 언제든지 TSMC에 기술력이 따라잡힐 수 있다.

시장조사업체 트렌드포스에 따르면 TSMC는 FO-PLP 개발을 위한 전담팀을 구성했고, 일찌감치 생산 준비를 하고 있다. TSMC는 포럼에서 대만 장비 등 반도체 업체들과 FO-PLP 협력을 논의할 전망이다.

앞서 TSMC는 FO-PLP의 이전 기술인 '팬아웃 웨이퍼레벨패키지(FO-WLP)' 기술을 업계 최초로 상용화할 만큼 패키징 기술력이 높다.

업계 관계자는 "올해 TSMC는 FO-PLP 개발에 총력을 기울이고, 양산 계획도 구체화할 전망"이라며 "삼성은 이번 대만 포럼에서 HBM과 FO-PLP 분야의 고객사들을 확보하는데 집중할 수 있다"고 전했다.

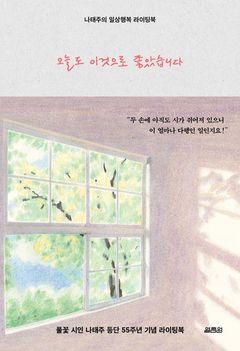

![[그래픽=뉴시스]FO-PLP 기술의 핵심인 직사각형 PCB 패키징 특장점.](https://img1.newsis.com/2024/06/28/NISI20240628_0001587944_web.jpg?rnd=20240628095344)

[그래픽=뉴시스]FO-PLP 기술의 핵심인 직사각형 PCB 패키징 특장점.

◎공감언론 뉴시스 [email protected]

Copyright © NEWSIS.COM, 무단 전재 및 재배포 금지